МИКРОПРОЦЕССОРНЫЕ УСТРОЙСТВА В РАДИОЭЛЕКТРОННОЙ АППАРАТУРЕ

МИКРОПРОЦЕССОРЫ — ЭЛЕМЕНТНАЯ БАЗА ЦИФРОВЫХ УСТРОЙСТВ

1.1. ПРИНЦИПЫ ПОСТРОЕНИЯ МИКРОПРОЦЕССОРНЫХ СРЕДСТВ

Микропроцессорные средства (МПС) возникли в результате развития технологии и вычислительной техники. По своей сути микропроцессор — это устройство, представляющее собой одну «ли несколько больших интегральных схем (БИС), выполняющих -функции процессора ЭВМ. Являясь частью вычислительных устройств, МПС используют и принципы их построения. Вместе с тем, существующий уровень развития полупроводниковой технологии вносит свои коррективы в эти принципы. Например, разрядность и сложность микропроцессорных (МП) БИС определяются максимальными размерами кристаллов, изготовление которых может обеспечить технология производства.

При построении современных МПС используют, в основном, «следующие принципы: микропрограммное управление, модульность построения, магистральный обмен информацией, наращиваемость вычислительной мощности.

Микропрограммное управление. Классическое вычислительное устройство состоит из арифметического устройства (АУ), устройства управления (УУ), запоминающего устройства (ЗУ) и устройства в во да-вывода (УВВ); АУ и УУ образуют процессор любой ЭВМ, т. е. ее управляющую и обрабатывающую части. УУ вырабатывает сигналы, под действием которых АУ выполняет все необходимые операции и действия. Существуют два метода построения УУ: с использованием комбинационных схем и микропрограммного ЗУ. В первом случае каждое входное воздействие »а УУ жестко связано с выходным и их изменения возможны только при изменении электрической схемы УУ. Поскольку входное воздействие — это команда МП, то использование такого метода жестко фиксирует его систему команд; при этом достигается максимальное быстродействие УУ. Микропроцессоры, использующие комбинационные УУ, называют МП с фиксированным набором команд. Примером такого МП является КР580ИК80.

В соответствии с микропрограммным принципом управления любая сложная операция делится на последовательность более простых действий.

Такое простое действие называется микрооперацией и выполняется за один такт работы АУ. Для задания очередности следования микроопераций вводятся специальные переменные, называемые логическими условиями. Совокупность микроопераций, выполняемых за один цикл (несколько тактов) работы устройства, называется микрокомандой (МК). Микрокоманда представляет собой двоичное я-разрядное слово, содержащее код операции (КОП), выполняемой АУ, а также коды адресов исходных данных и результата. Микрокоманда поступает на вход АУ, которое дешифрует ее и вырабатывает управляющие сигналы. Эти сигналы стробируются импульсами внутреннего блока синхронизации, который формирует временные такты выполнения микроопераций. Микрооперации жестко связаны со структурой АУ и не могут быть изменены.

После выполнения действия, определенного КОП, АУ информирует об окончании выполнения микрокоманды. Каждому АУ присущ только свой, конкретный набор МК, который называется системой микрокоманд.

Устройство, предназначенное для записи, хранения и считывания МК называется микропрограммным устройством управления (МУУ). В простейшем случае МУУ представляет собой БИС ПЗУ «ли ППЗУ, в которой записаны МК- Для считывания этих МК необходимо устройство формирования адреса, например счетчик. Любую операцию можно представить последовательностью МК (микропрограммой). Необходимо отметить два основных отличия микропрограммного управления от жесткого: смена выполняемой операции обеспечивается заменой микропрограммы; при считывании каждой МК требуется обращение к ПЗУ, что снижает быстродействие УУ. Итак, микропрограммное управление заменяет аппаратные средства программными и обеспечивает высокую гибкость, но при снижении быстродействия.

Минрокомандный уровень управления АУ является самым низким уровнем, доступным разработчику МПУ. Микрокоманда наиболее полно отражает структуру АУ, в силу чего реализация операций с помощью микропрограмм является оптимальной в смысле экономии памяти и повышения быстродействия.

Наряду с этим МК представляет собой достаточно мелкую детализацию выполняемой операции, например «обнулить регистр», «содержимое регистра переслать в аккумулятор» и т. д. Поэтому для программирования сложных алгоритмов, которыми являются алгоритмы обработки сигналов, потребовалось бы составить микропрограммы,, содержащие сотни, тысячи микрокоманд. Отладить такую микропрограмму очень сложно.

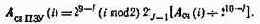

Для повышения уровня детализации выполняемой операции вводится командный уровень управления. Символом этого уровня является команда, которая представляет собой (как и микрокоманда) m-разрядное двоичное слово (обычно m<n). В общем случае формат команды должен включать КОП, адреса операндов, над которыми выполняется операция, и адрес результата. Команда представляет собой последовательность МК (микропрограмму). С целью экономии емкости микропрограммной памяти запись МК осуществляется в ячейки памяти, содержание которых, учитывает код текущей МК [1].

Рис. 1.1. Структурная схема микропрограммного устройства управления

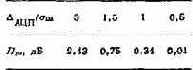

Структурная схема МУУ изображена на рис. 1.1. Команда, считанная из ЗУ, поступает на .регистр команд и далее на блок управления. В соответствии с принятыми сигналами блок управления формирует адрес первой МК микропрограммы, соответствующей принятой команде. Этот адрес через регистр поступает в ЗУ МК. Считанная из ЗУ МК состоит из двух частей: операционной (или собственно микрокоманды, которая поступает на АУ) и адресной, которая поступает на блок управления. Приняв адресную часть МК, блок управления формирует адрес следующей МК. Виовь считанная МК имеет свою адресную часть, которая поступает на блок управления. Этот процесс продолжается до тех пор, пока не будет считана последняя МК данной программы. После этого МУУ готово к приему следующей команды. Длина микропрограммы определяется разрядностью кода адреса следующей МК. В табл. 1.1 приведены типовые команды процессора, выполненного на микросхемах серии К589, и число МК, содержащихся в этих командах [4, 6].

Доля МК обращения к ЗУ составляет 20 — 40%, это дает возможность работать нескольким МП с общей памятью без взаимных помех.

Итак, использование микропрограммного управления при построении МПУ обработки сигналов позволяет разрабатывать системы команд и языки, ориентированные на структуру реализуемых алгоритмов, повышать быстродействие за счет параллельной работы нескольких микропроцессоров с общей памятью.

МИКРОПРОЦЕССОРНЫЕ УСТРОЙСТВА В РАДИОЭЛЕКТРОННОЙ АППАРАТУРЕ

ОСОБЕННОСТИ ПРИМЕНЕНИЯ И КОНСТРУИРОВАНИЯ ВСТРАИВАЕМЫХ В РЭА МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ

2.1. ОБЛАСТИ ПРИМЕНЕНИЯ КОНСТРУКТИВНО ВСТРОЕННЫХ В РЭА МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ

Развитие современной РЭА характеризуется широким применением цифровых -методов обработки, преобразования и регистрации сигналов. Устройства, входные и выходные сигналы которых представляются в цифровой форме, называют цифровыми. Элементной базой таких устройств являются цифровые ИМС различной степени интеграции.

Прогресс в области микроэлектроники привел к созданию микропроцессорных БИС, являющихся элементной базой построения нового класса цифровой РЭА — микропроцессорных устройств (МПУ), которые представляют собой функционально законченные, программно управляемые вычислительные устройства.

Чаще всего МПУ применяются совместно с цифровыми устройствами (жесткой логикой), расширяя функциональные возможности РЭА. Радиоэлектронные устройства (РЭУ) объединяют аналоговые, цифровые и аналого-цифровые узлы. Конструкция такого устройства обычно представляет собой моноблок [27]; МПУ, реализующие некоторые функциональные узлы РЭУ, встраиваются в него и конструктивно представляют собой одну или несколько функциональных ячеек моноблока |[28].

Области применения МПУ в современной РЭА определяются, в основном, их быстродействием и функциональными возможностями по сравнению с комбинационными устройствами. По мере изменения этого соотношения в пользу МПУ расширяются и области их применения. Исходя из современного уровня функциональных возможностей МПУ, можно выделить следующие области применения микропроцессоров в РЭА.

Цифровые системы радиосвязи. В цифровых системах радиосвязи находят применение широкополосные шумоподобные модулирующие сигналы. Использование таких сигналов позволяет рас-

средоточить энергию излучаемого сигнала в широком диапазоне частот, определяемом шириной спектра модулирующего сигнала. Рассмотрим пример использования микропроцессоров при построении таких систем [29].

Пример 2.1. Упрощенная структурная схема цифровой системы радиосвязи с широкополосными шумоподобными сигналами изображена на рис. 2.1. В данной системе связи низкочастотный входной цифровой сигнал модулируется высокочастотной псевдошумовой последовательностью. Ширина спектра промодулированного сигнала увеличивается пропорционально длине псевдослучайной последовательности. Такое расширение спектра позволяет рассредоточить энергию сигнала в широком диапазоне частот, что повышает отношение сигнал-шум при узкополосных помехах. Для демодуляции входного сигнала необходимо в приемном устройстве создать опорную псевдослучайную последовательность, идентичную модулирующей. После вычитания псевдослучайной последовательности из входного сигнала в высокочастотном демодуляторе-смесителе на выходе приемного устройства появляется исходный цифровой код данных.

Рис. 2.1. Структурная схема цифровой системы радиосвязи

Основной задачей схемы управления захватом, выполненной на базе микропроцессора СР-1600, является обеспечение и поддержание синхронизма друг относительно друга двух псевдошумовых последовательностей: принимаемой и опорной. На выходе детектора огибающей уровень сигнала будет нарастать пропорционально значению функции корреляции между двумя псевдошумовымв последовательностями. Этот сигнал, преобразованный в цифровую форму и усредненный по времени наблюдения, поступает на микропроцессор обработки, который работает в трех режимах: захват, проверка, поиск. Порог сравнения, соответствующий принятому режиму работы, устанавливается переключателем, входных уровней и через мультиплексор поступает в ОЗУ.

Программируемое ПЗУ емкостью 1КХ16 предназначено для хранения программ обработки входного сигнала. Код рассогласования, вырабатываемый микропроцессором обработки, поступает на регистр результата и буферные регистры. В соответствии с принятым кодом рассогласования дешифратор вырабатывает управляющее напряжение, которое осуществляет сдвиг псевдошумовой последовательности с целью получения максимальных значений напряжения на выходе детектора огибающей.

Точность синхронизации не превышает 1 бита. Микропроцессорная реализация схемы управления захватом обеспечивает выполнение трех режимов работы системы на одной и той же аппаратуре, возможность оперативного изменения длительности псевдослучайной последовательности и, следовательно, повышение помехоустойчивости системы связи.

Цифровая обработка сигналов (включая цифровую фильтрацию, спектральный анализ, корреляционную обработку и т. п.). Алгоритмы цифровой обработки сигналов основываются на вычислении операции свертки. Для вычисления операции свертки применяется, в основном, прямое и обратное дискретное преобразование Фурье (ДПФ). Для линейных дискретных систем с постоянными параметрами, к классу которых относятся цифровые устройства обработки сигналов, прямое и обратное ДПФ -может быть представлено в матричной форме [2]:

где Хn, Xk — матрицы-столбцы сигнала и его спектра размером. N; Fkn — унитарная матрица базисных функций размером NxN; F*kn — матрица, комплексно-сопряженная Fhn-

Для вычисления ДПФ в соответствии с (2.1) необходимо выполнить (N — I)2 умножений и N (N — 1) сложений комплексных чисел. Для уменьшения числа операций умножения и сложения

при вычислении ДПФ в практике проектирования цифровых устройств обработки сигналов используется алгоритм быстрого преобразования Фурье (БПФ) и его модификации [30].

Суть алгоритма БПФ заключается в том, что когда размер матрицы Fkn является составным числом, то матрица может быть представлена в виде произведения слабозаполненных матриц, т. е. факторизована. Это дает возможность производить вычисления ДПФ в несколько этапов, выполняя на каждом из них лишь небольшое число операций. Благодаря этому достигается экономия вычислений. Если N = rL, то г называют основанием преобразования, a L — числом этапов преобразования.

При цифровой обработке радиотехнических сигналов в качестве базисных функций чаще всего используются дискретные экспоненциальные функции вида

где Wh — дискретная экспоненциальная функция или поворачивающий коэффициент; iV — размер матрицы-столбца сигналов.

На рис. 2.2 изображен граф 8-точечного БПФ по основанию 2 с прореживанием по времени. Незачерченные кружочки обозначают операции сложения — вычитания, причем верхний выход означает сумму, нижний — разность. Стрелкой обозначена операция умножения на поворачивающий коэффициент. На графе можно выделить элементарный подграф базовой операции (при г = 2 это БПФ двух отчетов). Базовую операцию можно представить следующим образом:

причем X, У, А, В, Wh — комплексные числа.

Рис. 2.2 Граф 8-точечного быстрого преобразования Фурье (БПФ) (а)- базовые операции алгоритма БПФ с прореживанием по времени (б) и по частоте (в)

Блоки СОЗУ1, СОЗУ2 выполняют функции внутрипроцессорного интерфейса. На его вход поступают отсчеты входного сигнала с ОЗУ1, ОЗУ2 на первом этапе вычисления БПФ и промежуточные отсчеты с ОЗУЗ, ОЗУ4 назера-Бесселя [2]. Умножитель может быть реализован на БИС параллельных умножителей КР1802ВРЗ — КР1802ВР5. Максимально допустимое время умножения ty одного отсчета должно быть не больше, периода дискретизации Tn — 1JAF. Если Tд=(2-3) мкс, то целесообразно использовать 8-разрядный последовательный умножитель К.Р1802ВР2, потребляемая мощность которого ниже, либо умножитель К588ВР2, выполненный по КМОП-технологии.

«Взвешенные» отсчеты входного сигнала поступают на ОЗУ1 и ОЗУ2, емкость памяти которых определяется размерностью входного массива N:N= =Tc/Ta, где Tc — длительность обрабатываемого сигнала.

Сигналы, считанные из ОЗУ, поступают из вход МП БПФ, включающего сверхоперативные ОЗУ — СОЗУ1, СОЗУ2, МП БО, ППЗУ поворачивающих коэффициентов и выходные ОЗУЗ, ОЗУ4, остальных L — 1 этапах вычисления БПФ. С выхода СОЗУ отсчеты сигнала поступают на вход МП БО.

После вычисления ВПФ действительные и мнимые значения спектральных составляющих записаны в ОЗУЗ, ОЗУ4 соответственно. При приходе управляющих сигналов считывания эти значения через СОЗУ1, СОЗУ2 поступают на выход; СОЗУ1, СОЗУ2 npoVro реализуются на БИС обмена информации КР1802ВВ1.

Пример такой реализации для 8- разрядных магистралей показан на рис. 2.6. Разрешением обмена информации с каналами А, В, С, X управляют входы ЕСА, ЕСВ, ЕСС, ЕСХ. Выбор режима работы (считывание — запись) определяется сигналами RA, RB, RC, RX; WA, WB, WC, WX соответственно при разрешении обмена информацией с выбранным каналом. Входные сигналы ААО, АА1, АВО; АВ1, АСО, АС1, АХО, АХ1 обеспечивают выбор одного из четырех внутренних регистров БИС. Архитектура БИС ОИ обеспечивает помодульное наращивание разрядности выходных магистралей DA, DB, DC, DX. Магистрали DA, DB, DC предназначены для работы на короткие линии связи. Магистраль DX может работать на длинные согласованные линии связи (в данном случае выходные).

Рис. 2.4. Временная диаграмма работы микропроцессора базовой операции алгоритма быстрого преобразования Фурье

Рис. 2.5. Структурная схема вычислителя быстрого преобразования Фурье

Рис. 2.6. Функциональная схема СОЗУ, выполненного на БИС КР1802ВВ1

Используя МП БО и МП БПФ, можно построить различные цифровые устройства обработки сигналов.

Пример 2.4. Сигнал на выходе цифрового фильтра равен дискретной свертке входного сигнала s(nAT) с импульсной характеристикой системы h[nAT): y(nAT)=s(nДT)+h(nДT), где + — операция дискретной свертки. Известно, что свертка во временной области соответствует умножению в частотной области [30]. В соответствии с (2.1) получаем

Рис. 2.7. Структурная схема цифрового фильтра

На рис. 2.7 приведена структурная схема фильтра, реализующего алгоритм (2.3) и построенного на базе МП БПФ (см. рис. 2.5). Микропроцессор БПФ1 выполняет задачу спектрального анализа, т. е. переводит временной сигнал s(nAT) в частотную область. Далее вычисляется спектр выходного сигнала: Y(nAw). Микропроцессор БПФ2 выполняет обратное ДПФ, т. е. переводит сигнал из частотной области во временную. Как следует из (2.3), для реализации прямого и обратного ДПФ необходимы одинаковые функциональные блоки.

Рис. 2.8. Структурная схема адаптивного цифрового фильтра

Если вместо ЗУ импульсной характеристики использовать микропроцессор, вычисляющий ее значения, то получим адаптивный фильтр. Применяются такие фильтры при селекции движущихся целей на фоне отражений от поверхности Земли и метеобразований. Поскольку реальная окружающая среда отличается от предполагаемой, которая закладывалась в ЗУ импульсной характеристики, то характеристики реального синтезированного фильтра отличаются от оптимальных, что вносит потери. Эти потери можно скомпенсировать, если адаптивно реагировать на изменение окружающей среды. Структурная схемэ адаптивного фильтра изображена на рис. 2.8. Этот фильтр аналогичен фильтру, изображенному на рис. 2.7, за исключением того, что значения импульсной характеристики периодически пересчитываются в зависимости от окружающей обстановки.

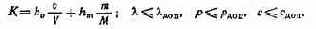

Управление лучом фазированной антенной решетки (ФАР) бортовой РЛС. Алгоритм управления лучом ФАР бортовой РЛС включает две части. Одна из них предназначена для вычисления направляющих косинусов по данным углового положения летательного аппарата в пространстве и предварительному указанию пеленга цели: (sd/Л)cos а и (sd/Л)cos$, где s — число состояний фазотаращателя; s = 2п/Дф (Дф — дискрет .приращения фазы); X — длина волны. Вторая часть алгоритма позволяет по полученным значениям направляющих косинусов рассчитать фазовое распределение в ФАР ![27]:

где (fij — значение фазы; ij — номер столбца и строки ФАР соответственно; (fa]mods — символ операции взятия целой части числа ПО МОДУЛЮ 5.

Анализ алгоритмов управления лучом ФАР показывает, что его первая часть содержит более 50% различных тригонометрических преобразований. Вычисление тригонометрических функ-

ций обычно осуществляется приближенными методами, использующими их разложение в ряд Маклорена. Вторая часть алгоритма, как следует из (2.4), по сути, (сводится к многократному повторению операции сложения, причем число операций сложения определяется размерностью модуля ФАР и равно псл = МхМ% М и N — число строк и столбцов ФАР соответственно.

Реализация такого количества сложений на МП, последовательно вычисляющем фij для каждого излучателя, привела бы к большим временным затратам. Поэтому целесообразно вычислитель управления лучом ФАР реализовать на МП с использованием аппаратного-сумматора, реализующего алгоритм (2.4).

Пример 2.5. Структурная схема вычислителя управления лучом ФАР приведена на рис. 2.9. Данные об угловом положении летательного аппарата и предварительное значение пеленга цели поступают через буферные регистры » ОЗУ. Микропроцессор в соответствии с программой, хранимой в ППЗУ, вычисляет значения направляющих косинусов для данного положения ЛА. Эти значения через буферные регистры подаются на сумматор, вычисляющий значения фазового распределения согласно (2.4). Структурная схема матричного сумматора для ФАР 8X8 приведена на рис. 2.10. Значения направляющих косинусов и сигналы управления поступают на буферный регистр, выполненный на БИС КР1802ВВ1, и далее на матричный сумматор, который вычисляет значения фij для каждого излучателя. Вычисленные значения хранятся в регистрах, а по сигналу считывания они поступают на фазовращатели ФАР. Общее время вычисления фазового распределения зависит от быстродействия сумматоров и приблизительно равно 9tсл.

Рис. 2.9. Структурная схема вычислителя управления лучом фазированной антенной решетки

Рис. 2.10. Структурная схема матричного сумматора 8X8

Комбинационные схемы. Микропроцессоры применяются для замены комбинационных схем, выполненных на ИМС средней и малой степени интеграции. Такие схемы в РТУ выполняют функции блоков синхронизации, .кодирующих и декодирующих устройств, устройств управления и т. п. Цифровые автоматы реализуются в основном на -матричных МП БИС типа ППЗУ и ПЛМ; при этом используются классические методы теории конечных автоматов. Методы синтеза конечных автоматов достаточно подробно освещены в .литературе. В [1] описывается система автоматизированного синтеза автоматов на матричных БИС.

Эта сис тема предназначена для синтеза автоматов, поведение которых описано граф-схемами алгоритмов (ГСА), в качестве элементной базы используются ПЛМ, ППЗУ, регистры, дешифраторы. При синтезе автоматов на этой системе необходимо учитывать следующие ограничения: общее число вершин ГСА не более 1023, число различных микрокоманд в ГСА не более 511, число различных микроопераций в ГСА не более 127, число внутренних состояний автомата не более 1023. Из приведенных данных видно, что сложность синтезируемых автоматов ограничивается несколькими тысячами внутренних состояний. При построении более сложных автоматов используются МП БИС совместно с комбинационными схемами. Типовой пример такого применения МП БИС приведен в [31]. Рассмотрим его подробнее.

Рис. 2.11. Функциональная схема программируемого синхронизирующего устройства

Пример 2.6. Функциональная схема программируемого синхронизирующего устройства приведена на рис. 2.11. Устройство выполнено на БИС К589ХЛ4 и представляет собой многофункциональное синхронизирующее устройство (D5 — D11).

В устройстве можно выделить следующие основные узлы: схему формирователя импульсов (D1 — D4), схему временной задержки (D5 — D7) и формирования частоты следования импульсов (D8, D9), формирователь числа импульсов в пакете (D10 — D11).

Схема формирования импульсов выполнена на микросхемах К500ТМ131 (D1), К500ПУ124 (D2), К500ИЕ136 (D3) и К500ПУ125 (D4). Устройство запускается подачей импульса «Пуск», а также управляющих и адресных сигналов на ППЗУ, поступающих с магистрали передачи информации (МПИ). При приходе сигнала «Пуск» триггер D1 устанавливается в 1; этот сигнал поступает на счетчик. Счетчик D3 работает в режиме деления частоты входных импульсов 80 МГц на 4, что достигается подачей кода ООП на его входы DO — D3. Неопределенность начала появления импульсов относительно сигнала «Пуск» не превышает периода следования импульсов кварцевого генератора 12,5 не.

Полученная последовательность ЭСЛ-уровня преобразуется в ТТЛ-уровень микросхемой D4.

С выхода D4 импульсы поступают на схему временной задержки. Выходной импульс длительностью 25 не появится на выходе F D7 через время задержки, определяемое из выражения Кп=2п — (t3 — tH)f, где t3 — время задержки; Кп — код пересчета (на входах D микросхем D5 — D7); тя и f — длительность и частота входных импульсов.

С выхода СО D7 положительный перепад напряжения устанавливает триггер D13 в 1, разрешая этим прием импульсов с f=20 МГц на схему формирования частоты следования импульсов (D8, D9). В зависимости от кода пересчета Кп, подаваемого на входы D микросхем D8, D9 изменяется частота следования импульсов, снимаемых с выхода F D9, по следующему закону: Кп = 2п — Kд, где Ад — коэффициент деления устройства.

Формирователь числа импульсов в пакете собран на элементах D10, D11. На его вход поступают выходные сигналы с D12. Число импульсов в пакете N определяется из выражения Кп=2n — (N — 1). После подсчета N импульсов на выходе F D11 появится сигнал, который своим фронтом через D2 установит триггер D1 в 0. При этом счетчик D3 перейдет в режим загрузки и работа всей схемы остановится.

Выбор необходимой задержки, частоты следования и длительности пакета импульсов определяется управляющим 28-разрядным кодом, считываемым из ППЗУ, по адресу, поступающему от микропроцессора с МПИ. Данное устройство позволяет устанавливать временную задержку 50 не — 204,8 мке, период следования импульсов 50 не — 12,3 мке, число импульсов в пакете 3 — 256. Устройство может применяться для управления работой АЦП, МП БО и др.

2.2. ОСОБЕННОСТИ ПРИМЕНЕНИЯ МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ В РЭА

При проектировании РЭА на МП БИС, в отличие от комбинационных цифровых устройств необходима совместная разработка программного обеспечения и аппаратных средств. Основные этапы проектирования МПУ приведены на рис. 2.12.

На этапе постановки задачи определяются входные и выходные требования к МПУ, математические методы решения поставленной задачи, разрабатываются алгоритмы решения задачи и взаимодействия МПУ с РЭУ.

Анализируя алгоритмы, решаемые МПУ и РЭУ, формируются требования и ограничения на их реализацию. Эти этапы являются типичными для любого РЭУ и поэтому обычно не вызывают затруднений.

Рис. 2.12. Основные этапы проектирования микропроцессорных устройств

На последующих этапах процесс проектирования раздваивается на аппаратурную и программную части. Первый же этап: выбор типа МП и структуры МПУ требует от специалиста знаний элементной базы МПУ, их систем команд, имеющегося программного обеспечения, средств отладки и т. п. На основе этих знаний осуществляется разбиение структуры МПУ на аппаратурную и программную части. Далее, исходя из выбранной структуры МПУ, конкретизируются требования к программному обеспечению и аппаратурным средствам. Осуществляется предварительная разработка программы и аппаратуры. Оцениваются основные характеристики МЛУ. Эти характеристики сравниваются с требованиями, предъявляемыми к МЛУ. Если полученные характеристики являются удовлетворительными, то осуществляется совместная отладка программного обеспечения и аппаратурных средств. По результатам отладки выпускается техническая документация.

Если характеристики не удовлетворяют требованиям, предъявляемым к МЛУ, выбирается другой МП или изменяется структура МПУ и весь процесс проектирования повторяется. Если для всего имеющегося в распоряжении разработчика набора МП и допустимых структур построения МЛУ не будет найдено удовлетворительное решение, то необходимо изменить требования, предъявляемые (К МПУ. Это достигается либо выбором более эффективных математических методов и алгоритмов, либо перераспределением задач между РЭУ и МЛУ.

В книге основное внимание будет уделено следующим этапам: выбору типа МП и структуры МПУ, предварительной разработки программного обеспечения и аппаратных средств, определению характеристик МЛУ. Этапы постановки задачи и формирования требований к разрабатываемым устройствам подробно изложены в специальной литературе, например [30, 32].

Отладка программного обеспечения рассмотрена в [9 — 11].

Кроме разработки программного обеспечения можно выделить еще ряд особенностей применения МПУ в РЭА: реальный масштаб времени обработки сигналов, использование аппаратных микропроцессоров, разработка специальных периферийных устройств и интерфейсных схем.

Реальный масштаб времени обработки сигналов (РМВ). Под РМВ обработки сигналов понимается необходимость обеспечения временного ограничения на выполнение алгоритма обработки сигналов: Тпр<Т, где Тпр — время выполнения программы микропроцессором; Т — допустимое время выполнения программы. Значение Гпр зависит от выполняемого алгоритма обработки, типа МП, его системы команд, структуры и т. п. Значение Т определяется структурой и требованиями к РЭУ, параметрами обрабатываемого сигнала. Для различных РЭУ и сигналов Т определяется по-разному. Рассмотрим, как определяется Т для МЛ БПФ (см. рис. 2.5).

Пример 2.7. Пусть МП БПФ решает задачу спектрального анализа сигнала, имеющего следующие параметры: полоса анализируемых частот AF= = 100 кГц, длительность обрабатываемого сигнала Гс = 10 мс. Требуется определить Т для МП БПФ и МП БО.

Для обеспечения РМВ необходимо, чтобы допустимое время спектрального анализа T<TCl т. е. время выполнения программы БПФ МП должно быть не более 10 мс. Частота дискретизации (при использовании квадратурных каналов) Fa=AF — l00 кГц. Размерность обрабатываемого массива N=2AFTC = =2-103. Число выполняемых БО NBQ=N/2*log2N=ll 103. Допустимое время выполнения одной БО ТБО <0,9 мкс. Микропроцессор БО (см. рис. 2.3) не обеспечивает решение данной задачи в РМВ. Поэтому необходимо использовать в МП БО вместо двух — четыре умножителя, либо в МП БПФ использовать несколько МП БО.

Допустимое время согласованной фильтрации более чем в 2 раза меньше-времени спектрального анализа, так как включает вычисление обратного ДПФ л умножение на импульсную характеристику. Параметр Т для МП управления лучом ФАР (см.

рис. 2.9) определяется максимально допустимым временем обнаружения цели T0: Т<Т0. Для других применений МП в РЭА Т определяется по-иному.

Использование аппаратных микропроцессоров. Для большинст ва задач обработки сигналов быстродействие микропроцессорных вычислителей недостаточно. Необходимо построение многомикропроцессорных систем. В |[2, 33] приведены примеры таких систем.

Существенное повышение быстродействия МПУ может дать применение аппаратных микропроцессоров, реализующих наиболее сложные, с вычислительной точки зрения, участки алгоритма обработки. Так, использование матричного сумматора в вычислителе управления лучом ФАР (пример 2.5) позволяет осуществить расчет фазового распределения за время, приблизительно равное 9tсл.

Возможны различные структурные варианты использования аппаратных микропроцессоров совместно с программными, некоторые из них приведены на рис. 2.13. В [2] приведены программы, реализации алгоритмов БО и БПФ для МП серий КР580, К589. В табл. 2.2 представлены данные о числе операций, используемых в алгоритмах, и времени вычисления этих операций.

Из табл. 2.2 видно, что умножение занимает значительную часть времени вычисления БО. Использование умножителей КР1802ВРЗ для вычисления БО позволяет снизить время ее вычисления для МП КР580 до 3082 мкс, для К589 до 20,4 мкс, для КР1802 до 1,5 мкс.

Рис. 2.13. Структурные схемы подключения аппаратных микропроцессоров к программным:

а — микропроцессор выполняет базовую операцию по программе, хранимой в ПЗУ; б — операция умножения выполняется аппаратно; в — базовая операция выполняется аппаратно

Этапы разработки ССИС

Приведем некоторые данные из программы разработки сверхскоростных БИС (ССИС) на основе МОП-приборов (табл. 2.4) [36].

Теоретически сокращение размеров в n раз приведет к повышению плотности компоновки в п2 раз. Однако из-за того, что с ростом числа элементов на кристалле растет и площадь соединений, плотность компоновки максимально повышается только в m раз (m<n2). Пропорционально с сокращением линейных размеров элементов в n раз уменьшаются значения токов и напряжений, а потребляемая мощность уменьшается в п2 раз.

Принципиальный недостаток сокращения размеров элементов -состоит в том, что в п2 раз повышается сопротивление соединений, что приводит к повышению плотности тока в n раз. Это может привести к миграции атомов металла проводника и другим вредным эффектам, снижающим надежность.

Наряду с повышением качества МП БИС, существенной проблемой улучшения конструкций МПУ является сокращение площади монтажных плат, занимаемой соединениями. Суть проблемы заключается в том, что с ростом степени интеграции площадь соединений на кристалле или подложке превышает площадь, занимаемую активными элементами. Наряду с этим, в [37, 38] показано, что без проведения оптимизации соединений в БИС процесс повышения степени интеграции практически будет приостановлен вследствие достижения логическими элементами своих физических пределов.

Повышение эффективности использования площади БИС и .подложек связано с решением задач совершенствования размещения элементов и трассировки связей на кристалле и подложке; оптимизации структурных и схемотехнических методов построения логических элементов в кристалле и БИС на монтажных платах.

Проблема оптимизации соединений свойственна конструкциям БИС, микросборок и ФЯ, тем более что для ряда устройств (например, ИЦП) эти конструкции близки.

Рассмотрим некоторые пути повышения эффективности использования плошади кристалла БИС. Полученные результаты во многом справедливы и для перспективных конструкций МПУ,

Для оценки качества размещения элементов и трассировки связей на кристалле БИС используют коэффициент оптимизации «связи К:

где Lcb, 1св(опт) — средняя длина линий связи при произвольном и оптимальном размещении элементов соответственно. В [37] показано, что

где N — число логических элементов на кристалле или степень интеграции; а — усредненный шаг размещения элементов на кри-сталле;

(SKp — площадь кристалла БИС). Подставив (2.8) в (2.7), получим

В табл. 2.5 приведены значения К для различной степени ин-теграции БИС.

Из табл. 2.5 видно, что с ростом степени интеграции N увели-чивается длина монтажных линий связи. Поэтому при конструи--ровании БИС и СБИС необходимо предусмотреть достаточную плошадь кристалла для выполнения межэлементных связей. Вели-чина этой площади зависит, в основном, от числа соединительных трасс или трассировочной способности кристалла БИС (Т):

где n — усредненная нагрузочная способность логического эле-мента, численно равная среднему числу входов логического эле-мента; n — коэффициент заполнения трасс кристалла; обычно среднее значение n = 0,5 — 0,7. Считая типовым случаем n = 0,5, a n = 3, получаем T = 2N5/6.

Площадь кристалла БИС для реализации межэлементных связей:

где ST — плошадь одной трассы. Для случая произвольного раз-мещения логических элементов при а= 1

где ят — шаг трасс.

Подставляя (2.10) в (2.9), получаем

Как видно из (2.11), с ростом степени интеграции увеличивается доля площади кристалла, отводимая под соединения между логическими элементами. Для. уменьшения этой площади необходимо повышать: качество размещения элементов на кристалле БИС, разрешающую способность технологии изготовления, число-слоев межэлементных соединений. Однако эти направления не смогут решить проблему роста площади соединений, поскольку имеют свои пределы.

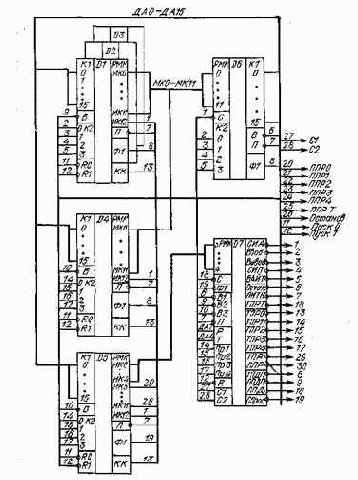

Новер линии

питания

ппд

Внутри и внепроцессорный обмен информацией осуществляется по асинхронному принципу с помощью сигналов «Выдано» (В) и «Принято (Я). При этом сигналы «Принято» всех БИС объединены, а «Выдано» соединяются следующим образом: В1 СК и В АУ, В2 СК и В D1 — D3, ВЗ СК и В D4 и DS, При таком соединении сигналов синхронизации обеспечивается разделение во времени приема данных и команд и запрещение приема команды в D1 — DS при наличии разрешенного прерывания. Соединением выводов С и Ф1 АУ и СК с соответствующими выводами управляющей памяти обеспечивается синхронизация передачи-приема МК.

Код состояния АУ выдается в канал К2 и далее поступает в канал К2 D1 — D3. В регистр состояния (канал K2) D4 и DS поступают сигналы прерывания СК Лр1 — Пр4.

Сигналы R0 и Rl D1 — D5 предназначены для начального запуска процессора. При ошибочном обращении к магистрали СК вырабатывает сигнал Я, который переводит D1 — D5 в режим формирования микропрограммы прерывания, вызванной этим ошибочным обращением к магистрали.

Интерфейс системной магистрали процессора включает 46 линий (табл. 1.3), 30 из которых (1 — 10, 18, 19, 29-46) по назначению совпадает с соответствующими линиями интерфейса микро-ЭВМ «Электроника-60». Остальные линии (11 — 17, 20 — 28) являются дополнительными.

Система команд процессора включает все команды микро-ЭВМ «Электроника-60», а также команды расширенной арифметики с фиксированной точкой. Для повышения производительности процессора в микропрограммах применено совмещение во времени отдельных этапов выполнения команд: считывание последующей команды совмещено с выполнением текущей, считывание данных из памяти — с не зависящими от него операциями. Применяемый в процессоре МПК БИС К588 электрически совместим с микросхемами серий 564 (при напряжении питания 5 В) и микросхемами серии 530 (при подключении не более двух нагрузок). Для повышения нагрузочной способности выводов внешнего интерфейса БИС процессора их можно подключать к системной магистрали через приемопередатчик К588ВА1, обеспечивающий согласование с 20 ТТЛШ-нагрузками и работу на емкостную нагрузку до 300 пФ. Потребляемая процессором мощность в динамическом режиме около 100 мВт.

Развитие МПК ведется в направлениях, указанных в 1.1, а также путем [совершенствования технологии МОП-структур, что постепенно выдвигает КМОП БИС и СБИС в первые ряды не только по малой потребляемой мощности, но и по быстродействию.

1.3. МИКРОСХЕМЫ ЗАПОМИНАЮЩИХ УСТРОЙСТВ

Основной элементной базой запоминающих устройств является полупроводниковая память, которую можно классифицировать по следующим основным признакам.

По функциональному назначению: сверхоперативная, оперативная, постоянная, буферная. Сверхоперативная и оперативная память предназначены для записи, хранения и считывания изменяемой информации (операндов, промежуточных результатов вычислений и т. п.). Принципиальных различий между сверхоперативной и оперативной памятью нет. Конструктивно оперативное ЗУ (ОЗУ) обычно выполняется в виде отдельного функционально и конструктивно законченного модуля, который подключается к интерфейсу [19]. Сверхоперативным ЗУ (СОЗУ) обычно называют регистры, конструктивно встроенные в МП БИС, например РОН БИС АУ (см. § 1.2). Время обращения к СОЗУ, как правило, не превышает одного такта работы МП. Поэтому при составлении программ стремятся максимально использовать СОЗУ, емкость которого из-за ограниченных размеров кристалла невелика (8 — 16 регистров). При отключении питания содержимое ОЗУ и СОЗУ теряется.

Для сохранения содержимого памяти при отключенном питании используют постоянное ЗУ (ПЗУ), которое предназначено-для хранения и считывания неизменяемой во время работы МПУ информации. В зависимости от способа записи информации различают: ПЗУ, программируемые маской, однократно программируемые пользователем (ППЗУ) и ПЗУ с многократной перезаписью информации, или репрограммируемые ПЗУ (РПЗУ) [4]. Первый тип ПЗУ используется при массовом производстве универсальных микро-ЭВМ, система команд которых не (изменяется. При разработке специализированных МПУ применяются ППЗУ и. РПЗУ, причем РПЗУ может применяться, например, на этапе отладки программы, когда вносится много изменений. Отлаженная программа записывается в ППЗУ и совместно с аппаратными, средствами представляет собой опытный образец разрабатываемого МПУ. Программирование ППЗУ осуществляется пережиганием, металлических или поликристаллических плавких вставок [4, 110].

Пережигание происходит при подаче импульсов напряжения соответствующей амплитуды и длительности на программирующие входы ППЗУ.В табл. 1.4 приведены режимы программирования наиболее распространенных биполярных ППЗУ.

Устройства, с помощью которых осуществляется запись (информации в ППЗУ, называются программаторами. В последнее время разработаны программаторы, работающие в автономном режиме или совместно с управляющей микро-ЭВМ [20].

solid windowtext

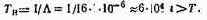

2. Полагая, что интенсивность отказов любой микросхемы равна 10~б, определяем время наработки на отказ МПУ:

3. Определяем среднее число выводов одной микросхемы и ее установочные размеры:

где ni — число микросхем i-го типа (i=1, 1); Kвыв i — число выводов микросхем i-гo типа; Квыв 1 — 38. Поскольку микросхемы устанавливаются в корпусах второго типа, имеющих шаг выводов 2,5 мм, считаем шаг установки средней микросхемы равным 50X38,5 мм, а ее размеры 40X28,5 мм.

4. Принимая размеры краевых полей x1, x2 y1, у2 равными соответственно-5, 5, 5 и 22,5 мм, определяем площадь печаткой платы, необходимую для размещения МПУ:

односторонняя компоновка

S1 = (3Ly + X1 + X2+ L0) (5by + y1 + y2 + bo) = 200X248,5 - 497 см»; двухсторонняя компоновка

S2 = (2Ly + X1 + х2 + Lo) (3bУ + у1 + у2 + bо) = 150x171.5 — 257 см».

5. Находим удельную мощность рассеивания МПУ: односторонняя компоновка

pi7K = 28,6/497 = 0,057 Вт/см2;

двухсторонняя компоновка

p2УД = 28,6/257 = 0,111 Вт/см2.

Сравниваем полученные значения с допустимым: р2уд>Рдоп. Корректируем значения: S2=28,6/0,08 = 357,5 см2 и Bп=357,5/171,5 = = 208,5 мм.

Параметры реализации

2. Используя выражения (3.6) и (3.10), определяем среднее время выполнения отдельных блоков алгоритма и частоту повторения этих блоков. Результаты расчетов сводим в табл. 3.10. Кроме того, считаем, что первый блок алгоритма может быть реализован на микросхемах К.573РФ4, К.573РФ6А. Вычисление БО выполняется на МП БО, представленных в табл. 3.7.

3. Анализ времени выполнения отдельных блоков алгоритма спектрального анализа показывает, что его реализация в реальном масштабе времени возможна только при распараллеливании вычислений. Для оценки этой возможности построим матрицу операндов, фрагмент которой приведен в табл. 3.11.

4. По данным матрицы операндов можно определить блоки алгоритма, допускающие их одновременное вычисление. В табл. 3.12 приведена последовательность вычислений отдельных блоков алгоритма.

Современный этап развития радиоэлектронной аппаратуры

Современный этап развития радиоэлектронной аппаратуры (РЭА) характеризуется широким применением методов цифровой обработки сигналов, реализуемых с использованием микропроцессорных средств. Однако ограниченные вычислительные возможности существующих микропроцессорных средств не позволяют обеспечить требуемые параметры реализации большинства алгоритмов обработки сигналов на одном микропроцессоре, что приводит к необходимости распараллеливания вычислений либо использования наряду с программными аппаратных средств. Выбор конкретной структуры построения микропроцессорного устройства обработки радиосигналов зависит от особенностей реализуемого алгоритма и конкретного набора микропроцессорных средств, на базе которых предполагается реализовать исходный алгоритм. Это порождает множество вариантов построения микропроцессорных устройств, выполняющих функции некоторой части РЭА.

За последнее время появилось много работ отечественных и зарубежных авторов, посвященных проектированию и применению микропроцессорных средств в различных отраслях техники, в том числе и в радиоэлектронике.

В данной книге приведены необходимые справочные сведения, методы и алгоритмы инженерного проектно-конструкторского синтеза микропроцессорных устройств обработки радиосигналов на ранних этапах разработки, включая по возможности весь комплекс вопросов от анализа заданного алгоритма до оценки конструктивных параметров его реализации на базе различных микропроцессорных средств. Предлагаемые алгоритмы формализованы и могут быть достаточно просто реализованы в виде пакета программ.

Большое внимание в книге уделяется вопросам создания специализированных вычислителей на комбинационных схемах или аппаратным процессорам, работающим совместно с программируемыми микропроцессорными устройствами. Показана эффективность этого известного приема для обеспечения высокой производительности устройств.

Ограниченный объем книги не позволил подробно рассмотреть вопросы разработки и отладки программного обеспечения МПУ. Эти вопросы изложены в [9 — 12].

Структурная схема формирователя адресов считывания ОЗУ и ПЗУ

Разрядность произведения выбирается с учетом требуемой точности реализации последующих вычислений. Так как в исходных данных эти требования не задавались, считаем достаточной разрядность произведения 8 бит. Итак, блок коррекции входных отсчетов может быть реализован на ПЗУ емкостью 4КХ8.

Таким образом, в результате анализа требований реализации исходного алгоритма установлено: для обеспечения заданного значения динамического диапазона выходного сигнала необходимо ввести этап коррекции действительной и мнимой частей входных отсчетов; внеполосное подавление до уровня — 43 дБ обеспечивается весовой обработкой входных отсчетов с помощью окна Хэмминга; система счисления с фиксированной запятой lк.ч=30; число отсчетов входного массива N=512; частота дискретизации fH>200 кГц; полоса пропускания эквивалентного фильтра Дf = 544 Гц.

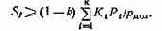

Построение различных вариантов реализации алгоритма спектрального анализа. С целью ограничения количества вариантов реализации используем метод отсечений, позволяющий исключать варианты, которые не могут привести к оптимальному решению. Критериями оценки вариантов являются ограничения на реализацию алгоритма спектрального анализа: Tс>2,5 мс, q>40 дБ, T>20 000 ч и руд<0,08 Вт/cm2, Fд>200 кГц и др. Возможность выполнения этих ограничений определяется характеристиками модулей МПУ: АЦП, МП, модулей ОЗУ, ПЗУ. Поэтому определим варианты реализации основных модулей МПУ.

Построение и выбор вариантов реализации АЦП. Для решения этой задачи иеобходимо определить допустимый для аналого-цифрового преобразования уровень потерь.

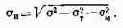

Известно [2], что динамический диапазон на выходе цифрового устройства обработки сигналов определяется следующим образом:

где d — динамический диапазон входного сигнала; Ку= 10 lg AfTc — коэффициент, характеризующий увеличение отношения сигнал-шум на выходе устройства; Пацп, Пбпф потери за счет аналого-цифрового преобразования и вычисления БПФ соответственно:

Будем считать, что П3ад<6,9 дБ, ПБПФ=10 лВ. В соответствии с методикой, изложенной в § 3.5, выбираем АЦП.

1. Так как FH>200 кГц, из табл. 3. 8 определяем, что для обеспечения П8>2 дБ допустимая длительность выборки: ф<0,36 Гп = 1,8 мкс.

2. Определим разрядность АЦП, обеспечивающую требуемый уровень яотерь:

где Пкв=Пзад — Пф =4,9 дБ.

3. Определенным в пп. 1 и 2 ограничениям удовлетворяют АЦП К1107ПВ1 и КП08ПВ1. Другие типы АЦП из дальнейшего рассмотрения исключаются.

Построение и выбор вариантов реализации МП осуществляется в соответствии с алгоритмом, рассмотренным в § 3.2. Модель алгоритма спектрального анализа приведена на рис. 3.12,6. Алгоритм содержит два цикла (х8 — Х12 и X7 — X14). Вероятность перехода рij между вершинами цикла p12,8=0,9961, p12,13=0,0039, а p14,7=0,89 и p14,15=0,ll. Другие значения рij=1.

Исходной элементной базой реализации МП являются данные таблиц 1.2, 3.5, 3.6 и результаты анализа алгоритма.

1. Определяем разрядность МП. Она рассчитывается исходя из требуемой точности представления информации на выходе МП. Однако, поскольку в данном случае принята система счисления с фиксированной запятой, считаем: 1=1 + L=15. В примере 3.1 было показано, что это значение превосходит I, вычисленное из условия обеспечения требуемой точности представления информации на выходе МП.

Содержание команды

Модульный принцип построения. Этот принцип предполагает разделение электрической схемы МПУ на функционально завершенные модули. Исходя из классической схемы вычислительногоустройства, любое МПУ должно включать как минимум микропроцессор, ЗУ и УВВ. Конструкция модуля представляет собой либо функциональную ячейку (ФЯ) (см. § 2.3), либо микросборку (МСБ), либо СБИС. Современные модули МПУ чаще всего выполняются в виде ФЯ. Приведенный выше состав модулей позволяет построить универсальное МПУ. При решении вопроса о функциональном составе модулей МПУ необходимо учитывать многофункциональность (универсальность) и специализацию модулей. Повышение универсальности модулей обеспечивает сокращение их. номенклатуры, снижение затрат на проектирование. Специализация модулей является средством достижения соответствия структуры МПУ выполняемым алгоритмам и тем самым повышения быстродействия, а следовательно, и эффективности применений1 МПУ в РЭА.

Модульный принцип конструирования МПС дает возможность, разработчику выбирать только необходимые ему модули и постепенно наращивать функциональные возможности МПУ. Иногда при проектировании МПУ, реализующих конкретные алгоритмы, для обеспечения требуемых характеристик достаточно небольшой фрагмент алгоритма реализовать аппаратно. Конструирование специального модуля или БИС для реализации такого фрагмента может оказаться неоправданно дорогим. Целесообразно на модуле МП установить специальный соединитель для подключения малых модулей, реализующих конкретные функции. Такой подход был реализован в микромодульных платах iSBX [3].

Для расширения функциональных возможностей одноплатной микро-ЭВМ разработаны три модуля: последовательного вводавывода iSBXx25i, параллельного ввода-вывода iSВХх350 и арифметического процессора с плавающей точкой iSВX332.

При менение таких модулей увеличивает гибкость одноплатной микро-ЭВМ. Для обеспечения аппаратной специализации системы разработана переходная плата iSBXyx960=5, содержащая пять гнезд шины iSBX, к которым разработчик может подключать специальные аппаратные модули.

Модульный принцип построения позволяет повысить эффективность применения МПС для конкретных задач. Это достигается выбором типа и числа модулей, учитывающих особенности решаемого алгоритма. Например, микро-ЭВМ «Электроника С5-12» в минимальной конфигурации представляет собой микропроцессор, содержащий ПЗУ емкостью 1КХ32 и ОЗУ емкостью 128X16. Микро-ЭВМ может использоваться совместно с модулями «Электроника С5-121» — АЦП (число каналов 115, время преобразования 10 мс, погрешность 0,4%), «Электроника С5-125» — модуль внешнего ОЗУ емкостью 8К байт, «Электроника C5-I123» — модуль сопряжения с устройством ввода-вывода и некоторыми другими.

Комбинируя модули, можно получать вычислительные средства различного назначения. Приведем некоторые из них: микро-ЭВМ+ +ОЗУ — минимальная конфигурация одноплатной микро-ЭВМ с относительно большим объемом памяти, микро-ЭВМ + АЦП — применяется в измерительных приборах, цифровых следящих системах.

Магистральный принцип обмена информацией. Некоторые выводы МПС должны соединяться с различными внешними устройствами. Это обеспечивается объединением выводов МПС в магистрали (шины) и мультиплексированием во времени обмена информацией между модулями. Весь информационный поток, циркулирующий в МПС, обычно разбивается на три группы: адреса, дан-яые и управление. В соответствии с этим выделяют шину данных, шину адресов и управляющую шину. Применяя последовательно временное мультиплексирование, можно построить МПС с трех-, двух- и однотипной структурой.

При выборе структуры МПУ необходимо учитывать следующее: при уменьшении числа шин увеличивается площадь кристалла или модуля, отводимая под функциональные элементы, и тем самым повышаются функциональные возможности МПС.

Вместе с тем применение временного мультиплексирования обмена информацией приводит к снижению быстродействия и необходимости использования дополнительных буферных регистров.

В некоторый период времени только два устройства могут быть одновременно подключены к шине. Одно из них — ведущее, другое — ведомое. Ведущим устройством обычно является МП. При обмене информацией между МП и ведомым остальные устройства, подключенные к шине, не должны им мешать. Такое раздельное использование шины достигается различными способами подключения к ней выводов устройств. Известны три способа подключения: логическое объединение, объединение с помощью схем с открытым коллектором и объединение с использованием схем с тремя состояниями [4].

Логическое объединение выполняется с помощью логических схем ИЛИ, И (рис. 1.2,а). На входы логических вентилей поступают информационные сигналы И1 — И4. Подключением этих сигналов к шине управляют сигналы У1 — У4, схема формирования которых приведена на рис. 1.2,6. На вход схемы поступают два адресных сигнала: Al и А2. Схема формирует четыре взаимоисключающих управляющих сигнала У1

— У4. (Вместо этой схемы может быть использован любой дешифратор типа 1 из и на два входа и более. Максимальное число подключаемых устройств определяется числом входов логического элемента ИЛИ.

Объединение с помощью схем с открытым коллектором предполагает электрическое соединение выходов нескольких логических элементов, как это показано на рис. 1.2,в. В схемах с открытым коллектором отсутствует .нагрузочный резистор. Выходы схем с открытым коллектором объединены с использованием общего нагрузочного резистора RK. Выходной сигнал равен 0, если сигнал на любом из объединенных выходов равен 0, и 1, если сигналы на всех объединенных выходах равны 1. По аналогии с реализуемой логической функцией такой способ подключения называют «монтажным ИЛИ», или «монтажным И». При поступлении на вход управляющего сигнала 1, на выходе схемы ИЛИ появляется 1 (независимо от значения информационного сигнала И); в результате общий выходной сигнал не меняется.

При ( низком уровне управляющего сигнала сигнал на выходе схемы ИЛИ равен информационному. Итак, если один управляющий сигнал равен 0, а остальные II, то общий выходной сигнал повторяет значение информационного входа схемы ИЛИ, имеющей низкое значение сигнала управления.

Для подключения устройств к шине с использованием схем с открытым коллектором требуется меньшее число логических элементов, чем при логическом объединении. Однако шины на схемах с открытым коллектором (как и шины с логическим объединением) имеют ограниченное применение. В основном, это обусловлено следующими причинами:

1. Значение выходного тока стандартной управляющей схемы, выполненной по ТТЛ-технологии, около 20 мА. Поэтому с помощью «монтажного ИЛИ» можно объединить сравнительно немного (не более 20) схем с открытым коллектором.

Рис. 1.2. Структурные схемы подключения выходов нескольких микросхем к общей шине:

а — логическое объединение сигналов; б — схема формирования управляющих сигналов; в — подключение с помощью схем с открытым коллектором; г — подключение с помощью схем с тремя состояниями

2. Нагрузочный резистор занимает место на плате и потребляет около 1 мА, когда шина находится в рабочем состоянии. Наличие этого тока еще больше снижает уровень сигнала в шине.

Объединение с использованием схем с тремя состояниями свободно от недостатков, присущих рассмотренным выше способам. На рис. 1.2,г нагрузочными являются транзисторы VT1 и VT3. На входы транзисторов подаются управляющие и информационные сигналы. Каждая пара транзисторов управляет подключением одного устройства. При подключении устройства к шине транзисторной парой управляет информационный сигнал. Например, при подаче лог. 1 на VT1 и лог. 0 на VT2 транзистор VT1 открыт, VT2 закрыт; на шине — лог. 1. Если на VT1 подается 0, а на VT2 1, то на шине — лог. 0. Одновременно значение управляющего сигнала на входах транзисторов VT3, VT4 равно 0.

Оба транзистора закрыты, и схема находится в третьем устойчивом состояния: «цепь разомкнута». В этом состоянии через схему протекает очень маленький ток. Шины с тремя состояними имеют следующие преимущества:

схема в состоянии «цепь разомкнута» потребляет ток не более 0,4 мА (схема с открытым коллектором около 2 мА), поэтому в схемах с тремя состояниями можно объединить гораздо больше выходов (до 50);

не требуется дополнительных логических схем. Микропроцессорные БИС имеют буферные схемы с тремя состояниями внутри кристалла, для этого предусматривается дополнительный вывод;

нет необходимости использовать нагрузочный резистор.

При разработке МПУ логическое объединение и объединение с помощью схем с открытым коллектором используются обычно при организации внутренних шин МП, модулей ОЗУ, ПЗУ и др. При организации внешних по отношению к МП шин обычно используются схемы с тремя состояниями.

Наращиваемость вычислительной мощности МП С. Основным отличием МПС от других изделий вычислительной техники является реализация их в виде одной или нескольких БИС. Современные уровни развития полупроводниковой технологии и материаловедения позволяют производить БИС на кристаллах площадью» до 50 мм2. Небольшая площадь кристалла приводит к необходимости расчленения МПУ на отдельные БИС. Факторами, ограничивающими функциональную сложность этих БИС, являются число выводов и потребляемая мощность. Последний фактор особенно важен для .быстродействующих МП БИС, выполненных по биполярной технологии.

Современные МПК БИС включают несколько десятков БИС различного назначения. Разрядность МП БИС обычно составляет 4, 8, реже 16 бит. Микропроцессорные БИС с ограниченной разрядностью называются секционированными. Обеспечение требуемой разрядности проектируемых МПУ достигается путем объединения необходимого числа БИС. При этом обычно не требуется дополнительных аппаратных затрат, достаточно только объединить соответствующие выводы и цепи сигналов переноса.

Более подробно этот вопрос будет рассмотрен в § 1.2. Детальный анализ проблем построения различных МПС на секционированном МПК БИС Ат2900 рассмотрен в [5].

Таким образом, основные принципы построения МПС: микропрограммное управление, модульность построения, магистралыклй обмен информацией и наращиваемость вычислительной мощности позволяют разрабатывать МПУ, структура, система команд, быстродействие и разрядность которых учитывают особенности реализуемых алгоритмов.

1.2. МИКРОПРОЦЕССОРНЫЕ КОМПЛЕКТЫ БИС

Микропроцессорные средства включают: МПК БИС, однокристальные и одноплатные микропроцессоры, микро-ЭВМ, микроконтроллеры, устройства ввода-вывода, хранения, отображения, коммутации информации и т. п. Основой построения МПС являются: МПК БИС, микросхемы запоминающих устройств и преобразования вида информации (АЦП, ЦАП).

Микропроцессорный комплект БИС представляет собой набор электрически совместимых цифровых БИС, достаточный для построения различных МПУ. Существующие МПК БИС можно разделить на две группы: с фиксированной системой команд и секционированные. Основное различие этих комплектов заключается в способе реализации устройства управления. В первом случае оно реализовано на комбинационных схемах и конструктивно объединено с арифметическим устройством в одной БИС. Это объединение представляет собой функционально законченный микропроцессор с фиксированной системой команд, ориентированной на широкий круг решаемых задач. Такие МПК обычно имеют стандартные отладочные средства и относительно развитое программное обеспечение, что обеспечивает их широкое применение.

Примером однокристального микропроцессора является центральный процессорный элемент КР580ИК.80. Особенности построения и реализации арифметического и управляющего устройств делают недоступным программисту микропрограммный уровень управления. Он оперирует командами, которые не может изменить. Вместе с тем проектирование конструктивно встраиваемых в РЭА МПУ предполагает их специализацию в соответствии с реализуемым алгоритмом.

Кроме того, как .будет показано в гл. 2, одним из основных требований, предъявляемых к МПУ, является реальный масштаб времени вычислений решаемых алгоритмов. Необходимость специализации системы команд и структуры проектируемых МПУ ограничивает применение однокристальных микропроцессоров в РЭА.

Основной элементной базой конструктивно встраиваемых в РЭА МПУ являются секционированные МПК БИС, у которых в отличие от однокристальных микропроцессоров управляющее устройство реализовано на принципах микропрограммного управления. Такой подход обеспечивает доступ разработчика к уровню микрокоманд, что позволяет изменять команды и соответствующие им микропрограммы исходя из решаемых алгоритмов. Секционированные МПК имеют различные системы команд, разрядность, типы интерфейса ввода-вывода и т. п. Проектируемые на основе секционированных МПК МПУ обладают большой гибкостью, так как расширение функциональных возможностей обеспечивается изменением отдельных микрокоманд или заменой всей памяти микропрограмм.

Построение арифметического устройства требуемой разрядности осуществляется объединением 4-, 8- или 16-разрядных процессорных секций. Микропрограммное устройство управления выполняется на одной или нескольких БИС. Соединив между собой несколько БИС микропрограммного управления, можно увеличить объем микропрограммной памяти. Объединение арифметического и управляющего устройств позволяет получить базовую структуру микропроцессора. Подключение к ней специализированных БИС ввода-вывода, вспомогательных аппаратных микропроцессоров и других специализированных микросхем приводит к повышению производительности МПУ.

Использование секционируемых МПК обеспечивает гибкость проектирования как по аппаратным решениям, так и по реализации требуемой системы команд. Однако при этом предполагается, что разработчик знает возможности и особенности всех микросхем, входящих в состав МПК, принципы объединения их в устройство, организацию синхронизации в устройстве; владеет методами разработки и отладки микропрограмм.

Вместе с тем работа на микропрограммном уровне создает и определенные трудности. Микропрограммный уровень определяется конкретными схемными решениями, поэтому программирование на этом уровне требует от разработчика знаний аппаратных особенностей МПК, учета временных соотношений и т. п. Кроме того, разработка оригинальной .системы команд приведет к необходимости проектирования дополнительных аппаратных средств и программного обеспечения, предназначенного для отладки программ. Это обуславливает увеличение сроков [разработки и повышение стоимости МПУ, проектируемых «а основе секционируемых МПК БИС.

Микропроцессорные комплекты БИС отличаются своими характеристиками, основными из которых являются: число БИС в комплекте, число внутренних магистралей, разрядность, система микрокоманд, число регистров общего назначения, число уровней прерывания, быстродействие, число буферных регистров (портов) ввода-вывода (Явв, ЯВЫв) и др.

Число БИС в комплекте во многом определяет функциональные возможности МПК. Наличие в составе комплекта разнообразных специализированных БИС позволяет проектировать функционально законченные МПУ при минимальном использовании микросхем средней и малой степени интеграции. Если число специализированных БИС в МПК ограничено, то некоторые функциональные узлы приходится проектировать на (микросхемах малой и средней степени интеграция, что снижает плотность упаковки МПУ и ухудшает его конструктивные параметры. Кроме того, использование специализированных БИС для аппаратной реализации некоторых сложных (с вычислительной точки зрения) функций повышает производительность МПУ.

Как было показано в § 1.1, число внутренних магистралей микропроцессорных БИС колеблется от одной до трех. При выборе МПК необходимо учитывать, что уменьшение числа магистралей снижает процент использования площади кристалла под магистрали, а также быстродействие этих микросхем.

Большинство современных МПК имеют разрядность 4, 8 или 16 бит.

Ограничение разрядности обусловлено размерами кристалла и технологическими допусками изготовления логических элементов. Биполярные секционированные МПК обычно имеют разрядность 4 и 8 бит. Разрядность МПК, выполненных по МОП-технологии, достигает 16 бит.

Система микрокоманд (как и число БИС) определяет функциональные возможности МПК. Системы микрокоманд распространенных МПК БИС, их (форматы, разрядность, особенности реализации подробно рассмотрены в [6 — 12]. Отметим, что при выборе типа МПК необходимо, чтобы его система микрокоманд соответствовала решаемому алгоритму. При этом особое значение приобретают микрокоманды, реализующие специальные функции, например умножение, деление, нормализацию чисел и т. п. Эти функции могут быть реализованы аппаратно на специализированных БИС, либо программно, например в МПК БИС КМ1804 [12]. Для ряда применений, не требующих высоких скоростей обработки информации, программная реализация специальных функций может оказаться предпочтительней, так как не требует дополнительных аппаратных затрат.

Число регистров общего назначения (РОН) определяет емкость внутренней сверхоперативной памяти МП и колеблется от 2 до 16. Увеличение числа РОН в МПК дает возможность хранить в них большее число исходных данных и промежуточных результатов вычислений. При этом в микропрограмме вычислений будут шире использоваться микрокоманды типа регистр-регистр, а следовательно, уменьшится число обращений к ЗУ. Быстродействие выполнения такой микропрограммы будет выше.

Прерывание представляет собой процедуру обмена данными с внешними устройствами. При этом инициатором обмена является внешнее устройство, которое посылает сигнал «Запрос на прерывание». Получив этот сигнал, МП приостанавливает выполнение основной программы и переходит к реализации специальной подпрограммы обмена, называемой подпрограммой обработки прерываний. Эта подпрограмма выключает ряд действий, описание которых можно найти в [10, 13].

Число уровней прерывания опре деляет число внешних устройств, способных обращаться к микропроцессору и обмениваться с ним информацией. Этот параметр имеет особое значение при использовании МПК для построения систем сбора и распределения данных, характеризующихся большим числом датчиков информации, имеющих различный приоритет.

Параметром, характеризующим быстродействие МПК, обычно является время цикла выполнения простейшей микрооперации. Поскольку микрокоманды состоят из последовательности микроопераций различной длины, то время цикла выполнения микроопераций дает очень относительное представление о реальном времени реализации микрокоманд. Один из методов определения времени выполнения микрокоманд приведен в Приложении. При совместном включении нескольких арифметических и управляющих устройств с различным быстродействием такт работы всего МПУ определяется длительностью такта устройства, обладающего меньшим быстродействием.

Число буферных регистров (портов) ввода-вывода является параметром, характеризующим структуру МПК БИС. Для секционированных МПК характерно использование многопортовых структур (обычно двух-трех). Увеличение числа портов ввода-вывода приводит к уменьшению длительности цикла выполнения микрокоманды, упрощает построение МПУ, реализованных по «конвейерной» структуре. Остальные параметры МПК такие же, как и у Других цифровых микросхем. Это прежде всего уровни напряжений логических сигналов (U0 и U'), потребляемая мощность, устойчивость к изменениям напряжения питания, коэффициент объединения по входу, коэффициент разветвления по выходу (нагрузочная способность), помехоустойчивость и др.

Функциональная сложность МПК БИС определяется максимальными размерами полупроводниковых кристаллов, изготовление которых может обеспечить современный уровень развития технологии. Небольшие размеры кристаллов (до 50 мм2) требуют упрощения структур и ограничения разрядности БИС.

Для опреде ления содержимого внутренних регистров МП требуются специальные программы, обеспечивающие вывод содержимого регистров из МП. Большее число выводов БИС упрощает разработку МПУ. Однако корпуса, имеющие большее число выводов, занимают большую площадь на плате. Ограниченное число внешних выводов приводит к необходимости использования одних и тех же выводов для нескольких целей, например для ввода и вывода данных.

При построении МПУ необходимо обеспечить электрическое сопряжение между микросхемами МПК БИС. Условиями правильного сопряжения являются одинаковые представления логических О и 1 (U°, U1) и обеспечение допустимой нагрузки на каждый выход. При построении МПУ на одном или электрически совместимых МПК БИС первое условие выполняется и задача электрического сопряжения сводится к обеспечению допустимой нагрузки на каждый выход. Для МПК, выполненных по биполярной технологии, это условна может быть записано в виде неравенства [4]

I1 макс<I1вых, I0макс <I0вых, (1.1)

где I1вых — значение тока, отдаваемого в нагрузку; I'макс — максимально допустимый ток нагрузки, при котором напряжение на выходе соответствует U1; I°ВЫХ — ток микросхемы; I°макс — максимально допустимый ток нагрузки, при котором напряжение на выходе соответствует U0.

Нагрузочная способность по переменному току МПК БИС, выполненных по МДП функционально-технологическому принципу, существенно ниже нагрузочной способности по постоянному току и фактически определяется максимальной емкостью Сн.макс, которую можно подключить к выходу схемы:

CД < Cн.макc, (1.2)

где Сн — емкость нагрузки, складывается из входных Свх и выходных Свых емкостей входов (выходов) микросхем, подключенных к данному выходу, и емкости монтажа См.

Для сопряжения МПК БИС, имеющих различные уровни напряжений логических сигналов, используются специальные схемы, называемые усилителями-трансформаторами уровней напряжений. Например, микросхема К1800ВА4 позволяет сопрягать МПК ЭСЛ и ТТЛ.

Наиболее распространенными являются цифровые микросхемы вообще и МПК БИС в частности, выполняемые по принципам транзисторно-транзисторной логики. Поэтому некоторые микросхемы, выполняемые по другим принципам, могут объединять в кристалле буферные трансформаторы уровней, обеспечивающие по выходу и входу ТТЛ-уровни напряжений логических сигналов.

В настоящее время отечественная промышленность выпускает различные МПК БИС. Технические характеристики и описания этих комплектов приводятся в [6, II4 — 16]. Из известных и освоенных в производстве МПК БИС для использования в РЭА наибольший интерес представляют МПК БИС серий К588, К1800, КР1802, КМ1804. Состав и основные характеристики микросхем, входящих в эти МПК, приведены в табл. 1.2. Подробное описание МПК БИС содержится в [54].

Микропроцессорный комплект БИС КР1802 выполнен по ТТЛШ-функционально-технологичеокому принципу. Электрически программируемая логическая матрица КР556РТ1 позволяет (разработчику записать в «ее оригинальную систему команд, в (Наибольшей степени учитывающую специфику конкретного применения. Наличие матричных умножителей КР1802ВРЗ — КР1802ВР5, а также сумматора на четыре входа обеспечивают значительное повышение производительности МПУ при выполнении арифметических операций. В § 2.1 приведены примеры построения некоторых устройств обработки сигналов на МПК КР1802. Важнейшими особенностями МПК (с точки зрения обработки сигналов) являются [16]:

многопортовая структура БИС. Микросхемы обработки (КР1802ВС1, КР1802ВР1, КР1802ВР2) имеют два порта ввода-вывода; БИС параллельных умножителей КР1802ВРЗ — КР1802ВР5 — три порта, БИС обмена информацией (ОИ) КР1802ВВ1 — четыре, а БИС сумматора — пять портов ввода-вывода. Через эти парты может одновременно осуществляться выборка операндов и выдача результатов обработки. Такая организация БИС ориентирована на эффективное выполнение двухопе-рандовых операций, составляющих большинство (до 80%) всех операций обработки;

использование регистров общего назначения вне обрабатывающих БИС обеспечивает большее быстродействие МПУ, объединяющих несколько разнотипных БИС обработки информации, а также расширяет возможности разработчиков в применении регистров для реализации различных системных функций;

обеспечение конвейерной обработки информации. В БИС обработки информации каждый порт ©вода-вывода имеет регистр, на котором фиксируются операнды или результат. Последовательное объединение этих БИС и управление их входами-выходами позволяет проектировать устройства с конвейерной организацией обработки. Это обеспечивает проектирование МПУ, быстродействие которых определяется временем одного цикла БИС (около 150 нс). Подробное описание МПК БИС КР1802 приведено в [6].

Микропроцессорный комплект БИС КМ1804 выполнен также по ТТЛШ-функционально-техналогическому принципу. Архитектура МПК предусматривает параллельное наращивание разрядности, микропрограммное управление, конвейерную обработку. Эти архитектурные особенности обеспечивают высокую гибкость применения МПК КМ 1804 при построении различных МПУ. В отличие от МПК КР1802 в составе МПК КМ1804 нет БИС, аппаратно реализующих арифметические операции. Вместе с тем МПК КМ1804 отличается большим функциональным разнообразием БИС и, что особенно важно, включает большое число БИС, предназначенных для построения интерфейсных схем ввода-вывода. Комплекты КР1802 и КМ1804 электрически совместимы. Совместное их использование позволит проектировать МПУ обработки сигналов, отличающиеся высокой производительностью и гибкостью. Комплект КМ1804 (является аналогом МПК Ат2900. Построение- различных МПУ на базе Ат2900 подробно рассмотрено в [5, 12].

СПИСОК УСЛОВНЫХ ОБОЗНАЧЕНИИ

d — динамический диапазон входного сигнала

FД — частота дискретизации

Fобр — интервал об;работки по частоте

H(пДw) — дискретная импульсная характеристика системы в частотной области

h(nДT) — дискретная импульсная характеристика системы во временной области

L — число этапов вычисления быстрого преобразования Фурье

l — разрядность микропроцессора

laцп — разрядность АЦП

N — размерность входного массива

р, Рдоп — удельная мощность рассеивания и ее допустимое значение

r — основание преобразования

S — площадь монтажной платы

S(nДw) — спектр дискретного входного сигнала

s(t), s(nДT) — непрерывный и дискретный входные сигналы

T — допустимое время выполнения программы микропроцессором

Tnp — время выполнения программы микропроцессором

Тс — длительность обрабатываемого сигнала

tу — время выполнения операции умножения

Y(nДw) — спектр дискретного выходного сигнала

ДF — ширина спектра анализируемого сигнала

Дf — полоса пропускания фильтра

бf — расстояние между центральными частотами соседних фильтров

б, бдоп — среднее квадрэтическое отклонение погрешности вычислений на выходе микропроцессора и его допустимое значение

кратная 4. Система команд по

|

Наименование |

Обозначение |

Тип корпуса |

Основные электрические характеристики |

Примечание |

|

|

16-разрядное наращиваемое АУ |

К588ВС1, К588ВС2 |

Серия K5S8 2124.42 — 1 |

Tц

= 1,0 мкс; 150 логических |

Uп = 5 В±10%. Система |

|

|

Наращиваемая УП |

К588ВУ1 |

2124.42 — 1 |

произведений |

1.1305.909 — 82 |

|

|

Арифметический расширитель |

К588ВР1А — К588ВР1Г |

2124.42 — 1 |

tу<5 мкс; 1=8 бит |

Пвв-выв = 2 |

|

|

Системный контроллер |

К588ВГ1 |

2124.42 — 1 |

Число входов прерываний 7 |

Тц=600 нс |

|

|

Многофункциональный буферный регистр |

К588ИР1 |

2121.28 — 4 |

Tц

= 150 не; l=8 бит |

Пвв=1; Пвыв=1 |

|

|

Магистральный приемопередатчик |

К588ВА1 |

2121.28 — 4 |

Tц=150 нc; l=8 бит |

Пвв-выв=2 |

|

|

Умножитель 16X16 |

К588ВР2 |

4118.24 — 2 |

ty=2 мкс |

Пвв-выв= 1 |

|

|

Кодер-декодер последовательного мультиплексного канала |

К588ВГЗ |

2124.42 — 1 |

Тактовая частота кодера 2 МГц, декодера 12 МГц |

Преобразует код «Манчестер 2» в последовательный униполярный |

|

|

АЛУ |

К1800ВС1 |

Серия К1800 2207.48 — 1 |

U„= — 5,2 В±5%; |

Аналог Мс10800 |

|

|

Микропрограммное устройство управления |

К1800ВУ1 |

2207.48 — 1 |

Uц= — 2 В±5%; Tц = 28 нс; l=4 бит |

Аналог Мс10801 |

|

|

Схема синхронизации |

К1800ВБ2 |

2120.24 — 1 |

Разрядность МК — 8 бит |

Аналог Мс10802 |

|

|

Схема управления ОЗУ |

К1800ВТЗ |

2207.48 — 1 |

1=А бит; Рп=1,6 Вт |

Аналог Мс 10803 |

|

|

Двунаправленный трансформатор уровней |

К1800ВА4 |

2103.16 — 1 |

t3>8 нс; Рп=0,7 Вт |

Аналог Мс1080А |

|

|

8-разрядное АУ |

КР1802ВС1 |

Серия КР1802 2206.42 — 1 |

Гц = 120 не |

Uи=5 В±10% |

|

|

Блок регистров общего назначения (16X4) |

КР1802ИР1 |

239.24 — 2 |

Гц=45 не |

Ри=1,4 Вт |

|

|

Арифметический расширитель |

КР1802ВР1 |

2206.42 — 1 |

Гц-90 не; г-16 бит |

||

|

Схема обмена информацией (4X4) |

КР1802ВВ1 |

2206-42 — 1 |

Гц = 60 не; Рш=1Л Вт |

Пвв-выв = 4 |

|

|

Схема интерфейса |

КР1802ВВ2 |

2206.42 — 1 |

Гц = 100 не |

Рп=1 Вт |

|

|

Электрически программируемая логическая матрица |

К.Р556РТ1, КР556РТ2 |

2121.28 — 1 |

48 логических произведений |

Pп= 0,8 Вт |

|

|

Умножитель последовательный (8X8) |

КР1802ВР2 |

2206.42 — 1 |

tт>1,0 мке; tД>1,8 мкс |

Пвв-выв = 2; Рп=1,5 Вт |

|

|

Умножитель параллельный (8X8) |

КР1802ВРЗ |

2206.42 — 2 |

tу=200 не; Рп = 3 Вт |

||

|

Умножитель параллельный (12X12) |

КР1802ВР4 |

2136.64 — 1 |

tу=200 не; Рп=4 Вт |

Пвв=2; Пвыв=1 |

|

|

Умножитель параллельный (16X16) |

КР1802ВР5 |

2136.64 — 1 |

ty=200 не; Рп=5 Вт |

Пвв=2; ПвыВ=1 |

|

|

Сумматор на четыре входа |

К.Р1802ИМ1 |

2207.48 — 1 |

tс

= 150 не |

Пвв=4; Пвыв=1 |

|

|

4-разрядная процессорная секция |

КМ1804ВС1 |

Серия КМ1804 2123.40 — 6 |

Uв=5 В±10%; Гц

= 110 не. Разрядность — кратная 4. Система команд по ОСТ 11.305.909 — 82 |

Аналог Ат2901 |

|

|

Схема формирования ускоренного переноса |

КМ1804ВР1 |

201.16 — 16 |

Аналог Ат2902 |

||

|

Схема управления последовательностью мк |

КМ1804ВУ1, КМ1804ВУ2 |

2121.28 — 1 2121.28 — 1 |

Аналоги: Ат2909 Ат2911 |

||

|

Схема выбора адреса следующей мк |

КМ1804ВУЗ |

201.16 — 16 |

16 инструкций |

Ат2918 |

|

|

Параллельный 4-разрядный регистр |

КМ1804ИР1 |

201.16 — 16 |

Гц=20 не; Рп=0,65 Вт |

Ат2918 |

|

|

4-разрядная процессорная секция |

КМ1804ВС2 |

2123.40 — 6 |

Число РОН 16 |

Ат2903 |

|

|

Схема управления состоянием и сдвигами |

КМ1804ВР2 |

2123.40 — 6 |

t3

— 60 не. Число шин 2 |

Ат2904 |

|

|

Схема управления микропрограммой |

КМ1804ВУ4 |

2123.40 — 6 |

Гц=95 не; Рп=1,7 Вт |

Ат2910 |

Микропроцессорный комплект БИС К1800 выполнен по ЭСЛ-функционально-технологическому принципу. Микросхемы отличаются повышенными быстродействием и потребляемой мощностью. Архитектура МПК К1800, как и предыдущих, обеспечивает наращивание разрядности, микропрограммное управление, конвейерную организацию вычислений. Отличительной особенностью ЭСЛ-комплекта является ограниченный функциональный состав БИС, что затрудняет построение законченных МПУ только на МПК К1800. Комплект БИС К1800 электрически совместим с цифровыми микросхемами серий К500, К1500. Наличие в составе комплекта двунаправленного транслятора К1800ВА4 позволяет использовать совместно с К1800 МПК БИС ТТЛШ, например КР1802, КМ1804. При построении МПК К1800 использовался ряд схемотехнических и конструктивно-технологических особенностей построения быстродействующих микросхем, что позволило достигнуть степени интеграции до 1000 логических элементов (ЛЭ) на кристалле, снизить потребляемую мощность до 4 — 5 мВт на один ЛЭ и обеспечить время задержки 1 — 1,5 не на один ЛЭ [16].

Рис. 1.3. Функциональная схема операционного устройства, построенного на МПК БИС К.Р1802